# Some Considerations for Optimal Efficiency and Low Noise in Large Power Combiners

Robert A. York, Senior Member

Abstract— This paper examines some relationships between important design parameters in large combiner systems and key performance objectives such as power, efficiency, noise, and graceful degradation. Results are derived for the combining efficiency of general combiner systems, and used to contrast spatial and corporate combiners and identify optimum combiner topology for a given device technology. The influence of array size on excess phase noise is quantified and shown to decrease with increase numbers of devices. Results are also presented for the degradation in combining efficiency due to statistical variations in amplifier characteristics, appropriate to large combiners, showing that phase errors are the dominant factor in power degradation.

*Index Terms*—Power combining, combining efficiency, power amplifiers, spatial power combining

### I. Introduction

High power levels can be achieved in microwave/RF systems by combining the outputs of a number of amplifiers with otherwise limited power-handling capacity. The individual amplifiers are assumed to have roughly identical characteristics, and the splitter/combiner circuits are designed for uniform phase and amplitude characteristics over all *N* ports in the frequency band of interest, where *N* is the number of amplifiers to be combined. The passive combiner structure should have the lowest possible loss for efficient collection of available power.

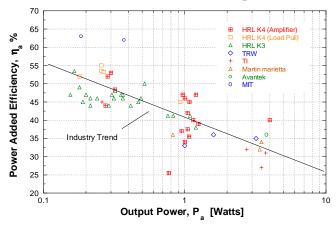

Figure 1 - Industry comparison of 18 GHz power devices [1].

To achieve a target power level, a designer will typically select the largest available power device (largest possible active die area) to minimize *N* and hence the complexity of the splitter/combiner

networks. However, this design practice should be reconsidered if high efficiency and low phase noise degradation are important objectives. It may be more advantageous to use a large number of smaller area devices to achieve a given power level, since the smaller devices often have significantly higher poweradded-efficiency (PAE) than large area devices (fig. There are other secondary benefits. devices yield better in production and hence can have lower overall cost. The excess phase noise through a combiner system is reduced by 1/N compared with the noise contributed by a single one of the component amplifiers—in other words, the degradation in phase noise through the amplifier can be reduced using a large number of amplifiers. Graceful degradation characteristics and tolerance of statistical device gain variations can also be improved using large numbers of devices. Small area devices also facilitate wideband circuit design, which may be advantageous in some applications.

To exploit these advantages requires an ability to combine *large numbers* of devices efficiently. Recent advances in spatial combining techniques offer an attractive means of doing so [2-5]. This paper examines some relationships between important design parameters in large combiner systems and performance objectives of combining efficiency, noise, and tolerance to device variations and failures.

## II. COMBINING EFFICIENCY AND PAE

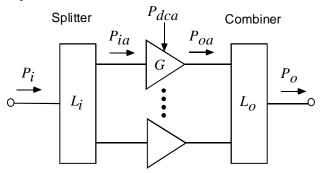

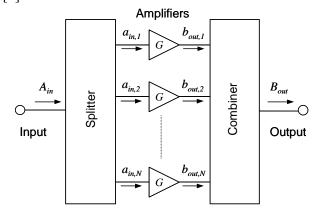

A general combiner system can be represented as in fig 2, with a lossy input distribution network, or "splitter", feeding a set of *N* amplifiers, and a lossy output combiner network.

Figure 2 - General N-way power combiner system.

The power transmission factor through the input and output splitter/combiner networks are described by  $L_i$  and  $L_o$ , respectively (e.g. a 3dB loss in the output network corresponds to  $L_o$ =0.5). Output losses determine the combining efficiency. Assuming a well matched and balanced combiner with identical devices, the combining efficiency is

$$\eta_c = \frac{P_o}{NP_{oa}} = L_o \tag{1}$$

Now consider the overall power-added efficiency (PAE). Each individual amplifier in fig. 2 has a PAE defined as

$$\eta_a = \frac{P_{oa} - P_{ia}}{P_{dca}} = \frac{P_{ia}(G - 1)}{P_{dca}}$$

(2)

For the purpose of this analysis, we consider this number to be fixed by the choice of device technology, or specification of the device size (fig. 1). The purpose of the combiner system is then to combine a large number of such amplifiers with the least possible degradation in PAE relative to  $\eta_a$ . Using the notation of fig. 2 and (2) we find an overall power-added-efficiency for the general combiner system given by

$$\eta_{sys} = \frac{P_o - P_i}{P_{dc}} = \frac{P_i(L_i G L_o - 1)}{N P_{dca}} = \frac{(L_i G L_o - 1)}{L_i(G - 1)} \eta_a$$

(3)

From this result we can see that as the individual amplifier gain G increases, the loss in the input network becomes less significant.

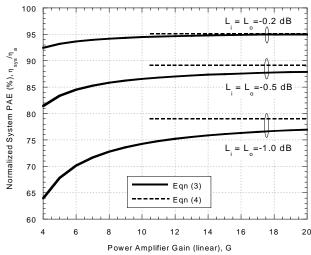

**Figure 3** - Normalized PAE of a combiner system versus amplifier gain from (3).

Fig. 3 displays the overall PAE normalized to that of a single amplifier ( $\eta_{sys}/\eta_a$ ), as a function of amplifier gain for representative values of splitter and combiner loss. In the limit of high gain we find

$$\eta_{sys} \to \eta_a \eta_c$$

(4)

For high gain the normalized system PAE asymptotically approaches the combining efficiency. High gain in the system can compensate for the effect of input losses on efficiency, and should therefore be an important design objective for efficient combiners. Note, however, that fig. 3 implicitly assumes the gain can be increased without increasing the DC power consumption of the array. Pre-amplifier stages, included either in each branch of the combiner or at the input of the splitter network, will increase the power consumption. However, since the pre-amplifier operates on a lower power signal, it should be possible to achieve the desired gain with a relatively small increase in power consumption relative to the power amplifier stage.

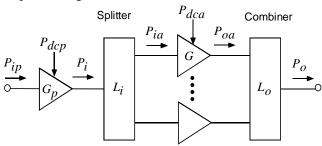

Figure 4 - General combiner system with pre-amplifier.

Consider the same power-combiner system of fig. 1 with a pre-amplifier at the input, as shown in fig. 4. Using the notation in the fig. 4, the overall system power-added efficiency can be expressed as

$$\eta_{sys} = \frac{G_p L_i G L_o - 1}{\frac{1}{\eta_a} G_p L_i (G - 1) + \frac{1}{\eta_p} (G_p - 1)}$$

(5)

where  $\eta_p$  is the PAE of the pre-amplifier defined as

$$\eta_p = \frac{P_{ip}(G_p - 1)}{P_{dcp}}$$

Note that when  $L_i = L_o$ ,  $\eta_p = \eta_a$ , and  $G = G_p$ , this expression reduces to

$$\eta_{sys} = \frac{GL_o - 1}{G - 1} \eta_a \tag{6}$$

which is the same as (3) in the limit of no input loss. Hence the system PAE should more rapidly approach the limiting value defined in (4) with the use of a preamplifier, even when the additional power consumption is accounted for.

Clearly the output loss is a valuable figure of merit for characterizing a power-combining system. From an experimental point of view it is usually easiest to measure the insertion loss through the entire passive network, which will include input and output losses. If the structure is symmetrical, a good estimate of the output losses can be obtained by halving the

insertion loss. Estimates of output combining losses from measured data are provided in [2,4] for a spatial power combiner using this technique.

#### III. INFLUENCE OF COMBINER TOPOLOGY

Spatial combiners are frequently argued to have potentially higher combining efficiency than transmission-line-based combiner systems. In fact, spatial combiners usually have poorer combining efficiency than transmission-line combiners when small numbers of elements are combined, owing to higher intrinsic losses in the passive structure, typically due to diffraction or higher-order mode excitation.

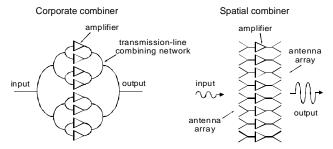

Figure 5 – Ideal binary-corporate and spatial combiners.

The real advantage of spatial combiner (and other parallel schemes such as radial combiner) systems is that the combining efficiency is approximately independent of the number of devices. Experimental evidence for the constant combining efficiency versus number of devices is presented in [4] for combiner systems with up to 32 channels. In contrast, some transmission-line combiner systems (such as the corporate binary-combiner structure, fig. 5) suffer an exponential decrease in efficiency with increasing numbers of devices. This implies a critical number of devices beyond which parallel combining is more efficient.

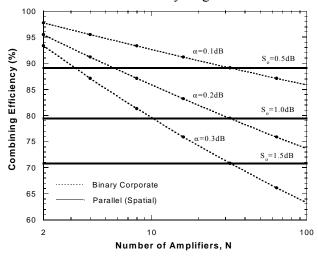

An ideal binary-tree corporate combiner has a total output loss given by  $L_o = \alpha^k$ , where  $\alpha$  is the loss-per stage, and  $k = \log_2 N$  is the number of stages. An ideal spatial combiner has a constant output loss  $L_o = S_o$ . Fig. 6 compares the maximum combining efficiency for these two cases. The critical number of devices at which the corporate and spatial efficiency curves intersect is easily found as

$$N_c = 2^{S_o[\text{dB}]/\alpha[\text{dB}]} \tag{7}$$

where the loss terms are in dB. For example, at X-band  $\alpha = 0.15$  dB is typical of a Wilkinson combiner, and  $S_0 = 0.5$ dB for a spatial combiner such as that described in [2-3]. Using these numbers, spatial combiners would be favored over a corporate

structure at  $N \ge 10$  for a given device. Note from fig. 6 and (7) that the intersection point is sensitive to small differences in the binary-stage loss  $\alpha$ .

Figure 6 – Combining efficiency versus number of amplifiers.

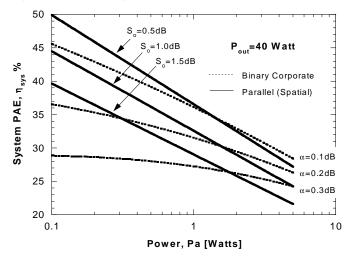

Fig. 6 and (7) are useful guides if the design objective is simply to maximize output power with the smallest number of devices. If design objectives include maximizing overall PAE, the influence of topology on is especially interesting when the trends of fig. 1 are accounted for. In this case, the problem to be addressed is as follows: given a range of available devices sizes  $P_a^{\min} \leq P_a \leq P_a^{\max}$ , a specified total output power  $P_{out}$ , and available combiner technologies specified by  $\alpha$  and  $S_o$ , what is the best choice of device size and combiner topology to maximize overall system PAE?

In view of fig. 1 and fig. 6, note that if the specified output power is so large that  $P_{out} > N_c P_a^{\max} S_o$ , then the spatial or parallel combiner topology will always be preferred, regardless of the choice of device. Expressed differently, this sets an upper bound on the device size that a spatial combiner must use to exceed the efficiency of a corporate combiner generating the same total power:

$$P_a \le \frac{P_{out}}{N_o S_o} \tag{8}$$

If  $P_{out} < N_c P_a^{\rm max} S_o$ , the trend of fig. 1 admits the possibility that a spatial combiner topology could still generate a higher efficiency than a corporate combiner, by using a larger number of smaller devices than the corporate combiner. For simplicity we model the empirical trends in fig. 1 using a linear approximation

$$\eta_a \approx A - B \log P_a \tag{9}$$

The straight line in fig. 1 corresponds to  $A \approx 41\%$  and  $B \approx 15\%$ . Using (9), we can compute a system efficiency from (4) for a specified power level as a function of device size. This is done in fig. 7, assuming a desired output power of 40 Watts at 18GHz, with devices ranging in size from  $P_a^{\min} = 0.1 \text{W}$  to  $P_a^{\max} = 5 \text{W}$  (fig. 1).

**Figure 7** – Overall system efficiency as a function of device size, using the data of fig. 1 and assuming a total output power of 40 Watts.

Fig. 7 is interesting in at least two respects. First, it demonstrates that the design practice of combining a minimum number of the largest available devices should be reconsidered, regardless of the choice of combiner topology, if maximum efficiency is an important objective. Second, under certain conditions a parallel combiner structure can exceed the performance of even the most efficient corporate combiner if a large enough number of small devices are used. This regime is described by (8). Naturally economic issues and size constraints, neglected here, will be an important factor in determining the optimal number of devices. However, since small-area devices are generally less expensive than large-area devices, it seems reasonable to expect that large combiners with small area devices can be costeffective.

# IV. PHASE NOISE IN COMBINER SYSTEMS

The use of large numbers of small devices in a combiner can have a positive influence on the noise properties of the system. In transmitter applications, particularly for certain types of radar, the amplifier should not seriously degrade the phase noise of the signal to be amplified, which is typically generated from a source that is phase-locked to a highly stable reference oscillator. The phase noise reduction can be derived as follows, which roughly parallels earlier

work aimed at noise reduction in oscillator systems [6].

Figure 8 – Generic combiner system for noise analysis.

With reference to the notation in fig. 8, we assume the input signal to be amplified is a noisy signal of the form:

$$A_{in} = A\cos(\omega t + \delta\theta_{in}) \tag{10}$$

where  $\delta\theta_{in}(t)$  describes the time-dependent phase fluctuations of the input signal. Assuming an ideal symmetric, broadband, linear power splitter for simplicity, the input signal to each amplifier in the array can be represented as

$$a_{in,i} = \frac{A}{\sqrt{N}}\cos(\omega t + \delta\theta_{in}) \tag{11}$$

The phase noise at the output of each amplifier is degraded, primarily from upconverted I/f noise, due to the nonlinear devices in the amplifiers. Amplitude noise in the bias supplies can also be upconverted to near-carrier phase noise. For our purpose the origin of the noise is unimportant, and we simply describe the total excess noise contribution of each amplifier by a time-domain fluctuation, so that

$$b_{out,i} = \frac{AG}{\sqrt{N}}\cos(\omega t + \delta\theta_{in} + \delta\varphi_{i})$$

(12)

(note G is now a voltage gain). The total output signal is then given by

$$B_{out} = \sum_{i=1}^{N} \frac{b_{out,i}}{\sqrt{N}}$$

$$= \frac{AG}{N} \sum_{i=1}^{N} \cos(\omega t + \delta \theta_{in} + \delta \varphi_{i}) \qquad (13)$$

$$= AG \cos(\omega t + \delta \theta_{out})$$

where

$$\delta \theta_{out} = \delta \theta_{in} + \frac{1}{N} \sum_{i=1}^{N} \delta \varphi_{i}$$

In deriving this we have assumed the phase fluctuations are small. We now assume that the input and amplifier noise sources are uncorrelated random (ergodic) processes with zero time average, and apply the Wiener-Khintchine theorem [7] to compute the power spectrum of the noise fluctuations. If the amplifiers have roughly the same noise power spectral density, the power spectral density of the output signal phase fluctuations (i.e. the *phase noise* of the output signal) will be given by

$$\left|\delta\tilde{\theta}_{out}\right|^2 = \left|\delta\tilde{\theta}_{in}\right|^2 + \frac{1}{N} \left|\delta\tilde{\varphi}\right|^2 \tag{14}$$

where  $\left|\delta ilde{ heta_{in}}

ight|^2$  represents the noise spectrum associated

with the input signal,  $\left|\delta\tilde{\phi}\right|^2$  represents the excess phase noise contributed by a single amplifier, and the tilde (~) denotes a Fourier transform (defined in the usual way for a random process). This result shows that the phase noise contributed by the amplifier ensemble is reduced by I/N as predicted. Intuitively, this is not surprising since the input signal being amplified adds coherently at the output, whereas the uncorrelated noise fluctuations add incoherently, and hence the peak amplitude of the carrier increases more rapidly than the noise skirts.

# V. INFLUENCE OF STATISTICAL VARIATIONS AND DEVICE FAILURES ON POWER AND EFFICIENCY

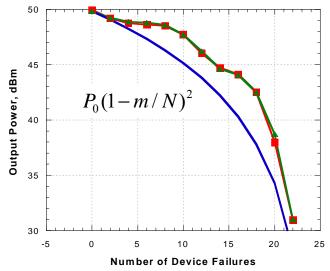

The influence of device failures on the power degradation characteristics of combiners has been addressed in [8]. In that work, it was shown that in a well-matched system, the reduction in power is expected to be proportional to  $(1-m/N)^2$ , where m/N is the fraction of failed devices. However, in most cases the system can actually perform better than this, depending on the impedance of the failed devices and the s-parameters of the combiner structure. This observation forms the basis of design schemes to improve graceful degradation performance (e.g. [9]). Recent measurements on laboratory combiner systems are shown in fig. 9 and confirm this point. Such graceful degradation characteristics are highly desirable in modern amplifier systems.

The efficiency of any real combiner is also limited by channel-to-channel uniformity. Gain and phase variations arising from device non-uniformities or manufacturing tolerances can lead to imperfect summation of power, and hence a reduction in combining efficiency. This problem has been nicely treated in [10], in which the *worst-case* combining efficiency is quantified for a specified maximum phase and gain variation. Knowledge of the worst-case efficiency can be useful for conventional combiners. For large combiners with essentially random gain and phase variations, the *probable*

efficiency is of interest, and a statistical treatment of the problem is appropriate. The problem is similar to the study of random errors in phased-arrays, and the following closely parallels the work of [11].

**Figure 9** – Measured data (previously unpublished) for the combiner system reported in [3], with device failures simulated by removal of bias ( $\blacktriangle$  and  $\Box$  denote two different shut-down sequences). The archetypal failure model [8] is shown for comparison (N=24).

Using the notation of fig. 8 we can write the output signal in phasor form as

$$B_{out} = \frac{AG_0}{N} \sum_{i=1}^{N} r_i (1 + \delta G_i) e^{j\delta \varphi_i}$$

(15)

where

$G_0$  is the nominal amplifier voltage gain

$\delta G_i$  is the *i*th-channel amplitude error

$\delta \varphi_i$  is the *i*th-channel phase error

$r_i$  represents statistical device failures

The amplitude and phase errors are again assumed to be independent random processes with zero mean. The probability of device survival is represented by  $P_e$  such that the  $r_i=1$  with probability  $P_e$ , or  $\left\langle r_i \right\rangle = P_e$ . The output power is proportional to  $P=B_{out}^2$ . If we denote the "no-error" output power as  $P_0=(AG_0)^2$ , then the relative change in the presence of errors is

$$\frac{P}{P_0} = \frac{1}{N^2} \sum_{i=1}^{N} \sum_{j=1}^{N} r_i r_j (1 + \delta G_i) (1 + \delta G_j) e^{j(\delta \varphi_i - \delta \varphi_j)}$$

(16)

Separating out the terms with i = j gives

$$\frac{P}{P_0} = \frac{1}{N^2} \left[ \sum_{i=1}^{N} r_i^2 (1 + \delta G_i)^2 + \sum_{i=1}^{N} \sum_{j=1}^{N} r_i r_j (1 + \delta G_i) (1 + \delta G_j) e^{j(\delta \varphi_i - \delta \varphi_j)} \right]$$

(17)

Now taking the ensemble average and assuming the individual amplitude and phase errors have the same variance (r.m.s. value) gives

$$\frac{\langle P \rangle}{P_0} = \frac{P_e}{N} \left( 1 + \langle \delta G^2 \rangle \right) + \frac{P_e^2}{N^2} \sum_{i=1}^{N} \sum_{\substack{j=1\\j \neq i}}^{N} \left\langle e^{j(\delta \varphi_i - \delta \varphi_j)} \right\rangle \quad (18)$$

where we used  $\langle r_i^2 \rangle = \langle r_i \rangle$  since  $r_i = 0$  or 1.

Assuming the phase errors have a normal (Gaussian) distribution, Skolnik [11] has shown that

$$\left\langle e^{j(\delta\varphi_i-\delta\varphi_j)}\right\rangle = e^{-\left\langle \delta\varphi^2\right\rangle}$$

so we find

$$\frac{\left\langle P\right\rangle}{P_{0}} = P_{e}^{2} e^{-\left\langle \delta \varphi^{2}\right\rangle} + \frac{1}{N} \left[ P_{e} \left( 1 + \left\langle \delta G^{2} \right\rangle \right) - P_{e}^{2} e^{-\left\langle \delta \varphi^{2} \right\rangle} \right] (19)$$

This is the desired result. The second term on the right becomes small for large N, so we see that the dominant effect is a power degradation due to device failures and phase errors. Large combiner systems can evidently tolerate significant amplitude errors as long as they have zero mean, but phase errors are particularly significant. For example, with an r.m.s. phase error of  $45^{\circ}$  the power in a large array would be reduced by nearly 3dB, seriously compromising combining efficiency and overall PAE. For small phase errors and  $P_{e} = 1$  we find

$$\frac{\langle P \rangle}{P_0} \approx 1 - \langle \delta \varphi^2 \rangle \tag{20}$$

Extra care should be taken to minimize phase errors between channels. This is especially difficult at mm-wave frequencies, and has led some workers to include variable phase-shifters in the combiner designs to compensate for device variations [12].

#### **ACKNOWLEDGEMENTS**

This work was funded by an ARO MURI program (grant #DAAG55-98-1-0001). The author wishes to acknowledge the help of former students Dr. Angelos Alexanian and Dr. Nai-Shuo Cheng who were very influential in the development of spatial combiners at UCSB. The author is also indebted to Dr. Michael Delaney at Hughes Space & Communications Division (El Segundo, CA) for contributing the empirical data on PAE vs. device size.

# REFERENCES

- [1] Data provided for publication by Dr. Michael Delaney at Hughes Electronics, Space and Communications Division, El Segundo, CA.

- [2] N.-S. Cheng, A. Alexanian, M.G. Case, D.Rensch, and R.A. York, "40 watt CW broadband spatial power combiner using dense finline arrays", *IEEE Trans. Microwave Theory Tech.*, vol. MTT-47, pp. 1070–1076, July 1999.

- [3] N.-S. Cheng, T.-P. Dao, M.G. Case, D.B. Rensch and R.A. York, "A 120-Watt X-Band Spatially Combined Solid State Amplifier", *IEEE Trans. Microwave Theory Tech*, vol. MTT-47, pp. 2557-2561, December, 1999.

- [4] P. Jia, L.-Y. Chen, N.-S. Cheng and R.A. York, "Design of waveguide finline arrays for spatial power combining", to appear in *IEEE Trans. Microwave Theory Tech*, 2001

- [5] R.A. York, "Quasi-optical Power Combining", Chapter 1 of *Active and Quasi-Optical Arrays for Solid-State Power Combining*, Wiley: New York, 1997.

- [6] H.-C. Chang, X. Cao, U.Mishra, and R.A. York, "Phase Noise in Coupled Oscillators: Theory and Experiment", *IEEE Trans. Microwave Theory Tech.*, vol. MTT-45, pp. 604-615, May 1997.

- [7] H. Stark and J.W. Woods, *Probability, Random Processes, and Estimation Theory for Engineers*, Prentice Hall: New York, 1986.

- [8] D.B. Rutledge, N.-S. Cheng, R.A. York, R. M. Weikle II, M.P.DeLisio, "Failures in power-combining arrays", *IEEE Trans. Microwave Theory Tech.*, vol. MTT-47, pp. 1077–1082, July 1999.

- [9] A.A.M. Saleh, "Improving the graceful degradation performance of combined power amplifiers", *IEEE Trans. Microwave Theory Tech.*, vol. MTT-28, pp. 1068–1070, Oct 1980.

- [10] M.S. Gupta, "Degradation of power combining efficiency due to variability among signal sources", *IEEE Trans. Microwave Theory Tech.*, vol. MTT-40, pp. 1031–1034, May 1992.

- [11] M. I. Skolnik, "Nonuniform Arrays", chapter 6 of *Antenna Theory*, *Part 1*, R.E. Collin and F.J. Zucker, eds., McGraw-Hill: New York, 1969.

- [12] P. Stenger et al., "A miniature, MMIC One Watt W-Band Solid-State Transmitter", 1998 IEEE Int. Microwave Symposium Digest, pp.